The HIGHER Project

European Heterogeneous Cloud/Edge Infrastructures for Next Generation Hybrid Services

Introduction to the HIGHER Project

The HIGHER Project brings together 11 partners from industry and academia to jointly develop and validate open-source designs for high-density rack-scale systems capable of supporting cloud and edge services at scale in standards-based data center environments. Starting with the ARM RHEA2 and RISC-V EPAC processors from EPI and the RISC-V EUPilot processor chip, the HIGHER Project adopts the Open Compute Project (OCP) Server family of standards to build processor modules for computation and acceleration, alongside a system security/control module, all operating with fully-featured operating systems and runtimes. The HIGHER Project aims to design OCP server mechanics to provide modular rack systems incorporating reusable standards-based infrastructure, encompassing hardware, low-level firmware, and systems software, ensuring trustworthy functionality for managing, securing, and controlling servers. The project’s open-source hardware and software outcomes will enhance European Digital Autonomy and facilitate wide adoption. Furthermore, the project will assemble representative software stacks supporting a range of use cases, including accelerated data processing and analysis for converged Cloud and HPC platforms, Infrastructure-as-a-Service with standardized management and monitoring, Platform-as-a-Service facilitating large-scale data processing for ML inference and data analytics, and memory pool management at the server rack level, with access control safeguards aligned with maturing CXL standards.

The HIGHER Project aims to develop and validate cloud and edge open-source European modules, technologies and complete systems developed based on open standard architectures, coupled with novel open-source runtime software stacks, capable of supporting efficient cloud and edge services and applications. It aspires to play a leading role in advancing the European ecosystem (including open-source HW and SW), providing an alternative to licensing intellectual properties from non-EU third parties, thereby enhansing European Digital autonomy.

Overall, the HIGHER Project will develop novel, mostly open-source, hardware and software modules and systems leveraging technologies developed, among others in the EPI and EUPilot projects, as well as standards established by the Open Compute Project (OCP), enabling the deployment of complete modular open cloud and edge infrastructures. HIGHER will further adopt a socket-based approach for EPI and EUPilot processor chips aiming at developing an EU socket reference, enabling interopperability and smooth processor upgrades.

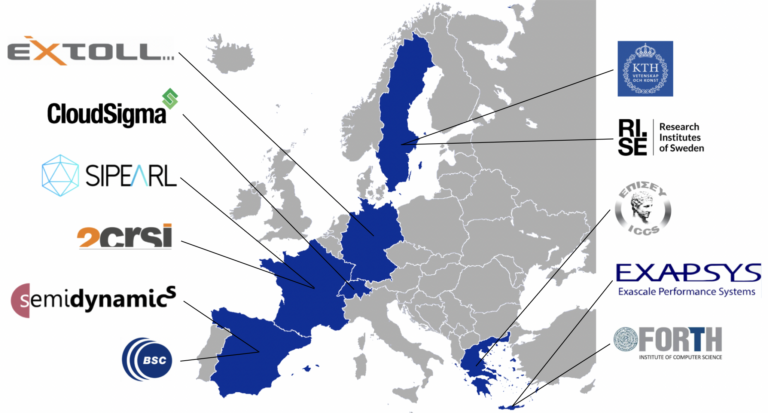

The HIGHER Consortium

The HIGHER Project consortium has significant competencies, not only covering, but also overlapping project needs to minimise risk. Each HIGHER partner has a clear role in the project, aligned with their expertise and individual exploitation plan.

HIGHER Partner Roles

FOUNDATION FOR RESEARCH AND TECHNOLOGY - HELLAS (FORTH)

Project coordinator, leads WP4 (Firmware System Software), with contributions to boot and OS support for HIGHER platforms. Contributes to platform development, leading the microserver I/O firmware task (T3.4). Leads the network object store use-case (T5.2)

EXASCALE PERFORMANCE SYSTEMS (EXAPSYS)

Leads WP3 (Hardware Platform Prototyping), with contributions to processor module designs. Responsible for the manulfacturing of HIGHER PCBs, component assembly and bring-up and testing tasks.

SEMIDYNAMICS TECHNOLOGY SERVICES (SMD)

Leads the EPAC/EUPILOT-based Processor Module (T3.2). Contributes to WP2 – Architecture and Verification.

BARCELONA SUPERCOMPUTING CENTRE (BSC)

Leads WP5 (Use Cases, Architectural Extensions and Evaluation), with contributions to the PaaS use case. Leads SW/HW Integration and Functional Verification (T2.3), and also the task on standards and Open Access Programme (T6.4).

SIPEARL (SIPEARL)

Leads WP2 (Architecture and Verification). Leads the requirements capture task (T2.1), RHEA 2-based Host Processor Module task (T3.1 and ARM secure boot and OS Task (T4.1). Contributes to the DC-SCM Management Module and Firmware development (T3.3). Responsible for providing dedicated Rhea2-based HPMs.

CLOUDSIGMA AG (SIGMA)

Leads WP6 (Dissemination, Exploitation, and Standardisation), with contributions to planning dissemination and communication actions, and tracking exploitation and use over the project lifetime. Leads the final evaluation task (T5.4).

EXTOLL GmbH (EXTOLL)

Leads the architecture and specifications task (T2.2). Contributes to HIGHER platform development, particularly to the use of high-speed links for interfacing among PCB components and with I/O peripherals.

RISE RESEARCH INSTITUTES OF SWEDEN (RISE)

Leads MetaOS (T4.3) and On-site evaluation (T5.5) tasks. RISE is a robust testing ground for emerging digital technologies as well as a European cloud representative which provides users with seamless access to a spectrum of digital services, ranging from Infrastructure as a Service (IaaS) to Platform as a Service (PaaS)

KTH ROYAL INSTITUTE OF TECHNOLOGY (KTH)

Leads accelerated data processing and analytics use cases (T5.1) in WP5, with dissemination and communication activities. Contributes to pilot applications that demonstrate the usage of HIGHER cloud servers, platform, and software.

INSTITUTE OF COMMUNICATION AND COMPUTER SYSTEMS (ICCS)

Leads the disaggregated memory activities (T5.4 with contribution to dissemination and communication tasks. Contributes to the pilot application that demonstrates the efficiency of CXL-based disaggregation of HIGHER servers.

2CRSI (2CRSi)

Leads Server Mechanics and Integration tasks (T3.4). Contributes to requirements and specification, particularly with respect to OCP chassis and rack design considerations.